著述大纲

DRAM概括

·动态随即存储器

·发展瓶颈

3D DRAM

·3D化DRAM

·DRAM结构尚需改进

DRAM时间发展前程

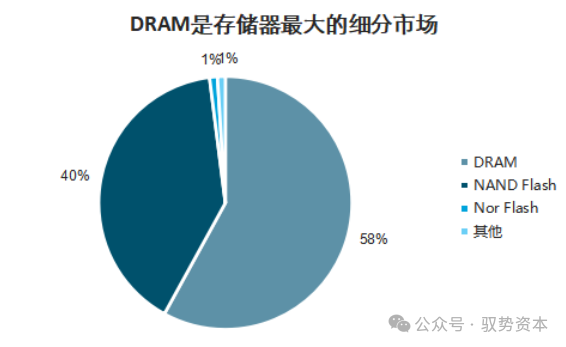

·DRAM贸易商场

·3D DRAM的时间挑战

·领头企业3D DRAM布局

DRAM

DRAM概括

1.1 动态随即存储器

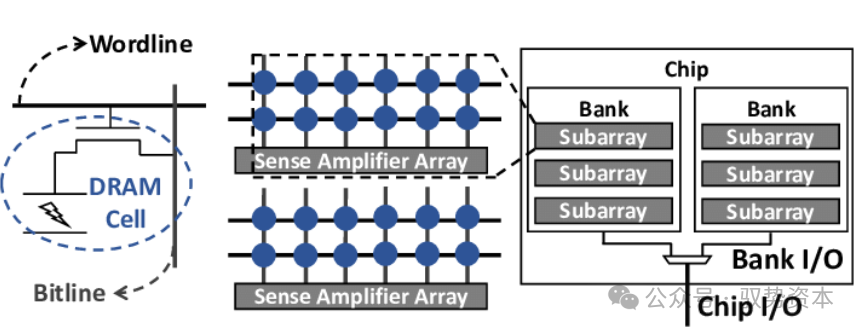

动态随即存取存储器(DRAM)的基本责任旨趣是通过存储单元中的晶体管和电容器来保存一个比特的信息(即0或1)。在DRAM中,基本的存储单元结构被称为1T1C,其中1T代表一个晶体管,1C代表一个电容器。晶体管在这里充任开关,按捺电容器是否允许电荷的流入或流出。电容器则负责执行的电荷存储,当电容器充满电荷时,暗意存储了一个1;反之,当电容器放电后暗意存储了一个0。

由于电容器的电荷会跟着时刻的推移渐渐暴露,因此DRAM需要通过周期性地刷新来保抓数据的线路性。刷新机制触及到按时地再行径电容器充电,以确保其能准确地响应存储的信息。这种不断刷新电荷的操作诚然保管了数据的好意思满性,但也带来了一定的功耗。

DRAM属于易失性存储器,这意味着它在断电后,存储的数据会迅速消散。因此,DRAM主要用于需要高速率造访和传输数据的场景,尤其是那些需要时时读取和写入的应用圭表。与其他存储时间比较,DRAM具有高速、容量大和相对低成本的上风,这使其成为当代电子开辟中的关节组件。

在执行应用中,DRAM普通用于个东谈主研讨机、就业器、智高手机、平板电脑等开辟中,主要负责存储临时数据。这些数据包括操作系统的中枢部分、正在运行的应用圭表数据以及用户的即时操作数据。由于DRAM的高速率秉性,它玩忽高效地处理多线程任务、及时研讨以及大限制数据操作等需要快速数据造访的场景。DRAM的发展伴跟着半导体工艺的不断开端,其存储密度和速率在徐徐莳植,而成本则相对保抓在一个较低的水平。这使得DRAM在研讨机边界的应用范围不断扩大,成为了撑抓当代研讨开辟性能的紧迫基础。

1.2 发展瓶颈

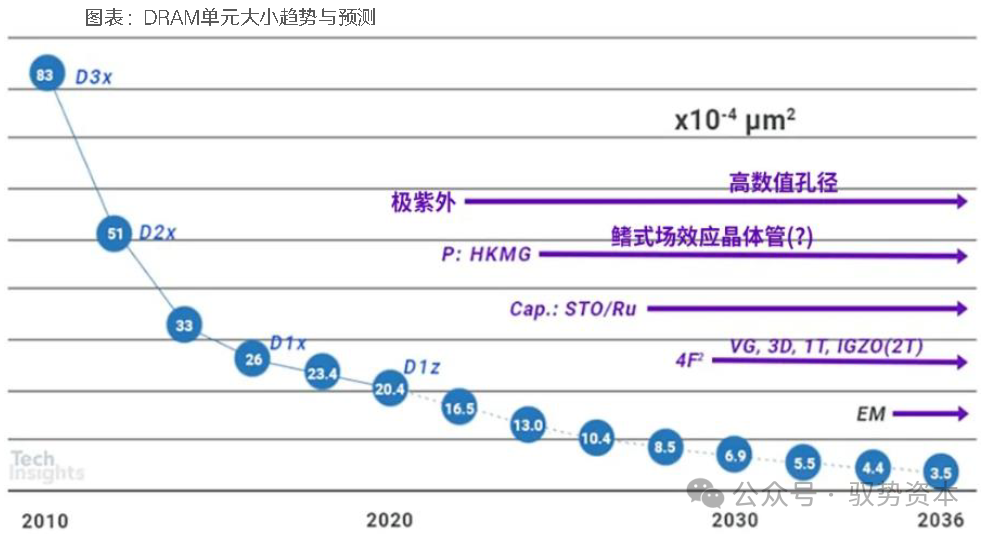

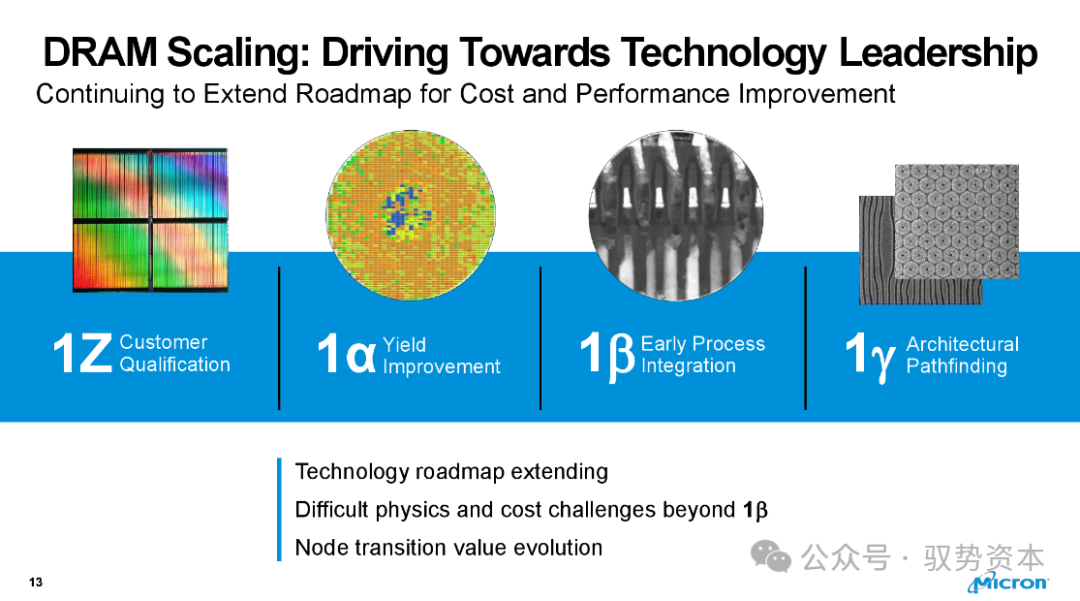

跟着摩尔定律的鼓动速率渐渐放缓,DRAM时间工艺正濒临越来越严峻的瓶颈期。在以前的几十年里,摩尔定律的推动下,半导体行业资格了马上发展,晶体管的尺寸不断缩小,芯片上的集成度越来越高,带来了更高的内存容量。然则,跟着晶体管尺寸接近物理极限,DRAM时间的开端速率也开动放缓,挑战愈发隆起。

从时间角度来看,晶体管尺寸的缩小意味着更多的晶体管不错集成到一派芯片上,这径直提高了芯片的内存容量。现时,DRAM芯片的制造工艺也曾打破到10nm级别,这是一个紧迫的时间里程碑,标明存储密度达到了前所未有的高度。然则,尽管10nm时间也曾取得了权贵的进展,它并不是DRAM发展的最终极限。改日的时间节点可能会不断向更小的尺寸鼓动,但这一进度伴跟着极大的时间挑战。

跟着DRAM制程节点的不断缩小,多个方面的挑战也更加彰着。开端是工艺好意思满性问题。跟着尺寸的减小,制造过程中的罪过容忍度越来越低,任何渺小的颓势都可能导致晶体管失效,影响通盘芯片的性能。其次是成本问题。制造更小尺寸的晶体管需要更复杂的工艺和更上流的开辟,这使得分娩成本权贵增多。特别是在现时内行半导体枯竭的配景下,成本问题显得尤为隆起。

电容器走电问题也跟着尺寸的缩小变得更加严重。DRAM依赖电容器来存储电荷,但当电容器变得更小,电荷暴露的风险增多,从而导致数据的可靠性下跌。为了惩办这个问题,工程师们需要开发新的材料和设计递次,以减少走电率并提高数据保抓智商。另一个首要挑战是侵略问题。在高集成度的芯片上,不同存储单元之间的电场和磁场侵略变得更加时时,这可能导致数据特殊或损坏。为了搪塞这一问题,需要更加复杂的特殊纠正机制和抗侵略设计,这进一步增多了DRAM开发的难度。

跟着DRAM时间线宽进入10nm范围,电容器走电和侵略等物理按捺问题变得更加隆起。这些问题不仅源于晶体管尺寸的缩小,还与一系列物理极限密切关连,如量子隧穿效应的增强、走电流的增多以及热线路性的下跌等。这些物理效应在超小尺寸的晶体管中愈发彰着,导致DRAM存储单元中的电荷保抓智商大大申斥,进而影响数据的可靠性。此外,跟着电介质厚度的减少,电容的值也随之减小,这进一步加重了泄走电流的增大,导致数据保抓时刻裁汰。

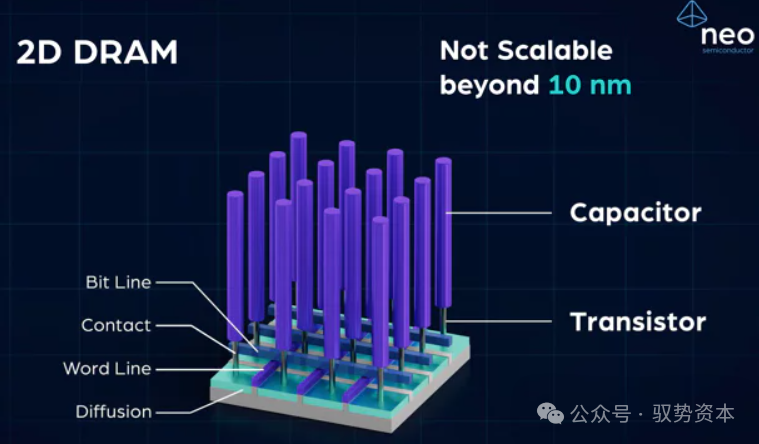

除了物理极限,材料科学的挑战也日益严峻。举例,传统的硅基材料在超小尺寸下性能下跌,电介质材料的厚度减少导致电容器的性能下跌。为了搪塞这些挑战,制造工艺的精密按捺条目变得更加严格,任何渺小的工艺偏差都可能导致存储单元的失效。因此,不断沿用二维(2D)款式缩悭吝件尺寸,尤其是在所谓的4F²缩放(即通过减少晶体管占用面积来增多存储密度)时,遭受了严重的时间壅塞。

为了打破这些瓶颈,产业界开动引入新材料和新时间,举例high-k电介质材料和极紫外(EUV)光刻开辟。High-k材料通过提高电介质的介电常数,不错在不增多电容器尺寸的情况下莳植其电容值,从而缓解由于电介质厚度减少带来的电容下跌问题。EUV光刻时间则通过使用极短波长的光束,玩忽在更小的圭表上进行精确的图案刻蚀,使得更高密度的晶体管布局成为可能。然则,这些新时间的引入并非莫得代价。它们平素伴跟着盛大的研发插足和制形成本,同期也对工艺按捺提倡了更高的条目。

跟着2D DRAM缩放难度的增多,通盘产业在研发插足、制形成本以及良率按捺方面的问题日益隆起。时间节点的进一步微缩诚然不错在单元面积内增多更多的比特存储容量,但所需的投资却呈现非线性增长,而性能莳植和成本勤俭却无意玩忽达到预期的后果。这种成本效益的失衡,意味着不断沿用传统旅途进行DRAM缩放在经济上变得不再可行,成为产业中难以藏匿的财务难题。

DRAM

3D DRAM

2.1 3D化DRAM

在现时东谈主工智能(AI)应用海浪的推动下,对高性能存储器的需求抓续攀升,HBM(高带宽存储器)看成DRAM边界的开端时间,备受商场追捧。然则,跟着商场需求的不断扩大,存储器厂商们正酝酿新一轮的DRAM时间“创新”,以更好地鼎沸改日的需求。HBM时间也曾开启了DRAM的3D化进度,使其从传统的二维(2D)结构向三维(3D)发展。然则,尽管HBM具备一定的3D秉性,它并弗成皆备被认定为确切的3D DRAM时间。

在3D DRAM的研发过程中,三星的4F Square VCT DRAM时间也曾展现出与3D DRAM主见更为接近的秉性。这种时间通过垂直堆叠存储单元,权贵增多了单元面积的存储容量,并莳植了存储遵守。与传统DRAM的水平甩掉存储单元不同,3D DRAM通过垂直堆叠的款式,玩忽在有限的芯单方面积内集成更多的存储单元,从而极地面提高了存储密度和性能。这种时间不仅为提高存储器容量提供了新的旅途,也为改日高性能研讨场景下的存储需求打下了坚实的基础。

诚然三星的4F Square VCT DRAM为3D DRAM的发展指明了标的,但它并不是3D DRAM时间的独一形态。存储器厂商们对3D DRAM的发展有着更加各种化的设计,包括探索不同的材料、结构和制造工艺,以进一步优化存储性能和成本效益。在这些设计中,3D DRAM不单是局限于现时的时间主见,而是将跟着时间的开端,徐徐演变为更加锻真金不怕火和多功能的存储惩办有研讨。

目下,3D NAND Flash也曾达成了贸易化应用,何况在存储商场上占据了紧迫地位。然则,3D DRAM时间仍处于研发阶段,但其改日前程深入。跟着AI、大数据等边界的烦闷发展,对大容量、高性能存储器的需求将大幅增多,3D DRAM有望成为改日存储器商场的主流家具。比较于传统DRAM,3D DRAM不仅在存储密度和速率上具有权贵上风,而且在能耗和成本按捺方面也展现出精良的后劲。

3D DRAM时间的发展将成为存储器商场的关节趋势之一。它不仅玩忽鼎沸现时商场对高性能存储器的需求,还将推动通盘半导体行业的时间开端。跟着时间的徐徐锻真金不怕火和应用场景的不断扩大,3D DRAM有望不才一代研讨架构中占据中枢肠位,成为推动AI、云研讨和大数据等前沿边界发展的紧迫引擎。存储器厂商将不断在这一边界插足多数资源,推动时间的打破与创新,为改日数字天下的存储需求提供强有劲的支抓。

2.2 DRAM结构尚需改进

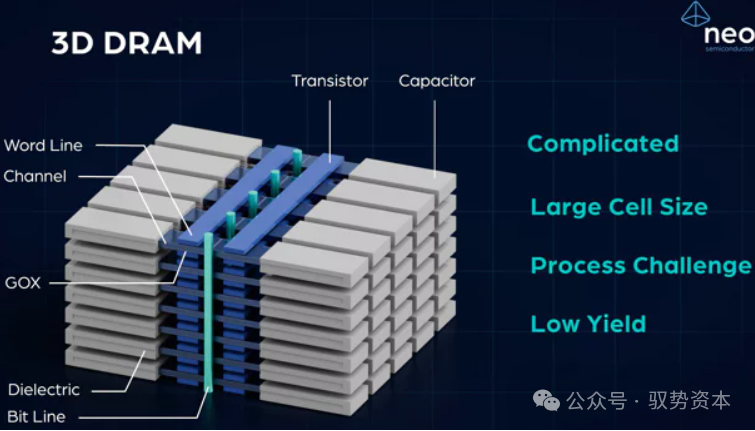

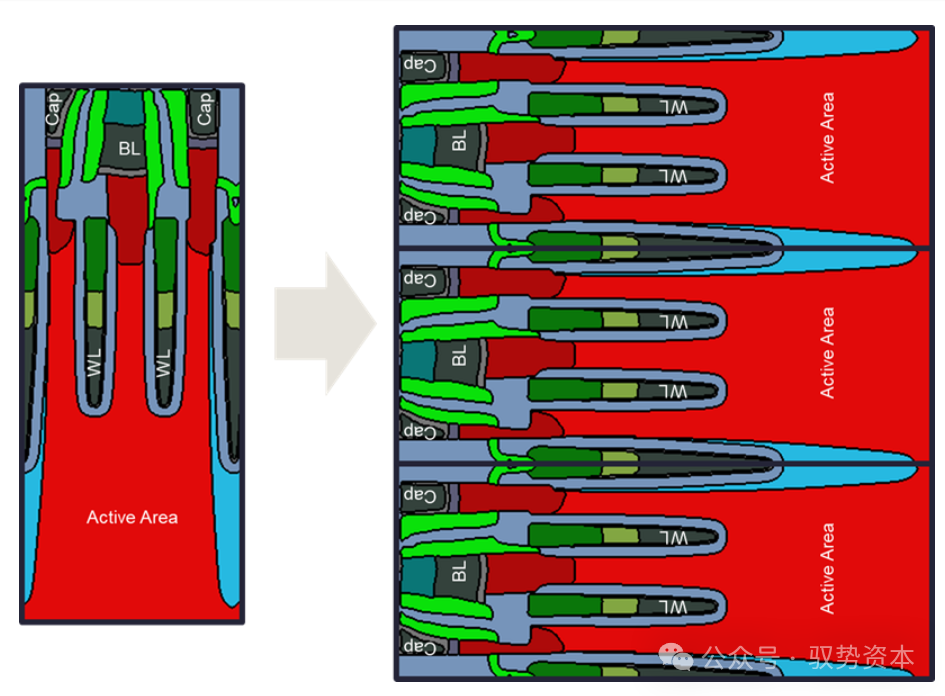

(1)为了鼓动DRAM的微缩进度,将传统的二维(2D)DRAM组件侧放并进行垂直堆叠成为一种关节策略。然则,这一递次在执行应用中遇到了多种时间挑战。开端,堆叠过程中触及的水平标的刻蚀极为谨慎。由于凹槽尺寸存在权贵各别,横向刻蚀的精确按捺变得复杂,这可能影响结构的好意思满性和性能。其次,在堆栈刻蚀和填充过程中,需要使用不同的材料,这增多了制造工艺的复杂性。此外,纠合不同3D组件时,还存在集成难题,如安在保抓性能的同期达成线路的纠合成为关节。

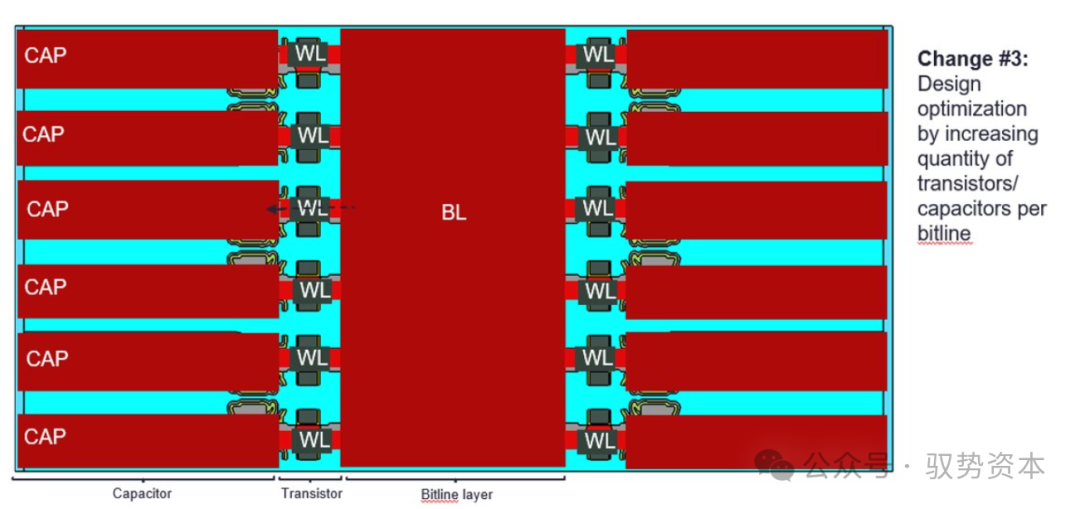

为了搪塞这些挑战,时间上遴选了一些创新的递次以莳植DRAM的微缩智商。开端,裁汰电容器的长度并将其垂直堆叠是提高存储密度的有用款式。传统上,电容器的长度和高度额外,但通过裁汰电容器长度,不错在有限的空间内增多更多的存储单元,从而提高单元面积的存储容量。为达成这少量,设计中将位线移到纳米薄片的另一侧,使得电流不错通过晶体管栅极穿过通盘纳米薄片。这么作念不仅增多了电容器工艺处理的空间,还有用减少了硅区域的占用面积。

其次,遴选了栅极全包围晶体管时间,以进一步缩小硅的有源区面积。这种设计优化了空间欺诈率,使得玩忽在更小的区域内集成更多的晶体管。此外,通过将也曾又窄又高的电容器设计为短而宽的结构,进一步优化了电路布局。这一改进收获于将位线移至架构的中心位置,从而开释出更多空间供电容器和晶体管使用。

在此基础上,通过在位线斗殴点两侧甩掉更多的晶体管和电容器,达成了更高的集成度。这种再行设立的纳米薄片不错进一步堆叠,从而增多每个位线斗殴点上的晶体管和电容器数目。在初度迭代中,垂直堆叠的3D DRAM结构不错达到多层高度,比现存的工艺节点高出数个级别,权贵提高了存储密度和容量。跟着堆叠层数的增多,DRAM的存储密度将进一步提高,鼎沸改日高性能研讨和大数据处理对存储器的需求。

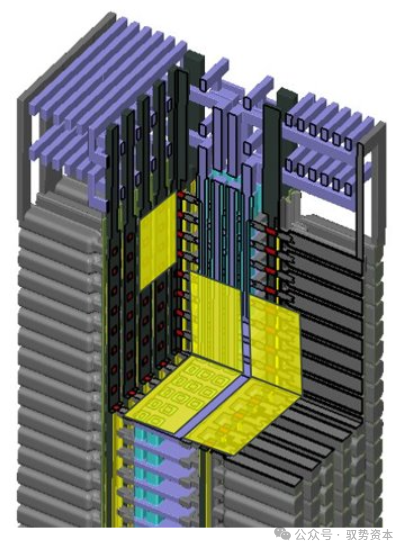

(2)3D DRAM的发展不仅需要全新的架构设计,还必须在金属化和纠合性上进行首要改进。为了在垂直方朝上达成存效的电流传输,工程师们探索了几种新递次,这些递次使得电流不错通过中央的位线堆叠,股票融资进而激活特定的存储层。其中一种递次是欺诈水平的MIM(即金属-绝缘层-金属)电容器阵列来纠合各层存储单元,同期引入栅极全包围(Gate-All-Around, GAA)结构,将栅极材料皆备包裹在硅晶体管周围。当电畅达过这些位线时,惟有指标层的位线被激活,确保电流玩忽精确地纠合到所需的晶体管,从而达成精确的读写操作。

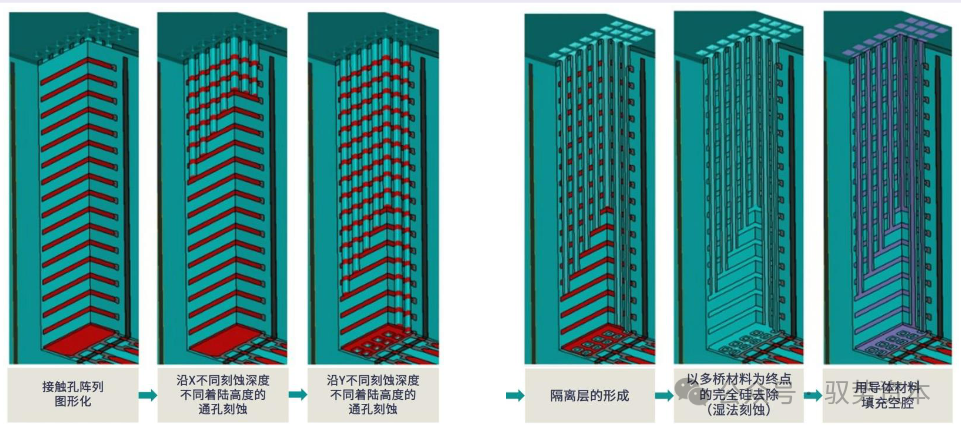

3D DRAM的关节组件包括多层堆叠的栅极全包围纳米薄片硅晶体管、位于两排晶体管之间的位线层、24根垂直字线位线、各层之间的互连水平,以及MIM电容器阵列。这些设计不仅提高了3D DRAM的存储密度,还增强了其性能和遵守。为了克服传统3D NAND中台阶式结构的局限性,3D DRAM引入了一种新式的通孔阵列结构。这些通孔穿过硅堆栈层,并在特定的存储层住手,形成每层一个通孔的私有设计,使得斗殴点不错径直位于存储单元里面。这种结构简化了3D DRAM的纠合性,同期提高了制造的可控性和线路性。

在执行制造过程中,沟槽制作是一个关节格式。开端,制作沟槽并在侧墙上引入阻遏层,然后欺诈高沟槽结构引入刻蚀介质以去除毋庸要的硅材料。接下来,将导电金属填充到空的沟槽中,形成有用的电流传导旅途。这一过程确保了3D DRAM中的每个存储单元都能被精确按捺和操作,从而提高了合座的存储密度和性能。

由于3D DRAM的制造工艺与3D NAND有好多相似之处,因此3D DRAM的存储密度展望将跟着3D NAND层数的增多而同步莳植。换句话说,3D DRAM的执行密度在很大程度上取决于同期3D NAND时间的开端。这种关联性使得咱们不错笔据现存的3D NAND时间阶梯图,对改日3D DRAM的存储密度作念出合理的预测。跟着3D NAND时间的不断开端,3D DRAM也有望在改日达成更高的存储密度和更强的性能弘扬,鼎沸高性能研讨、大数据处理和东谈主工智能等边界对存储器日益增长的需求。

DRAM

DRAM时间发展前程

3.1DRAM贸易商场

3D DRAM的上风不仅在于其更大的容量,还体目下其超卓的数据造访速率上。传统的DRAM在读取和写入数据时,需要经过多格式的操作经过,这平素包括数据的选址、存取和刷新等操作,这些格式可能会导致造访速率的按捺。然则,3D DRAM通过垂直堆叠的存储单元结构,使得数据不错更加径直地读取和写入。这种垂直造访款式权贵简化了数据流动旅途,减少了蔓延,极地面提高了数据造访速率,从而在高性能研讨和及时处理当用中展现出权贵的上风。

除了速率上的莳植,3D DRAM还具备低功耗和高可靠性的秉性。在传统DRAM中,为保抓数据的线路性,电路需要时时刷新,导致了较高的功耗。而3D DRAM由于其高效的存储单元结构和优化的电流旅途设计,不错大幅申斥功耗,从而更顺应于移动开辟、镶嵌式系统等对能耗敏锐的应用场景。此外,3D DRAM的垂直堆叠设计使得其在更小的空间内容纳更多的存储单元,这不仅提高了存储密度,还增强了其抗侵略和耐用性,从而确保在恶劣环境下依然玩忽线路责任。

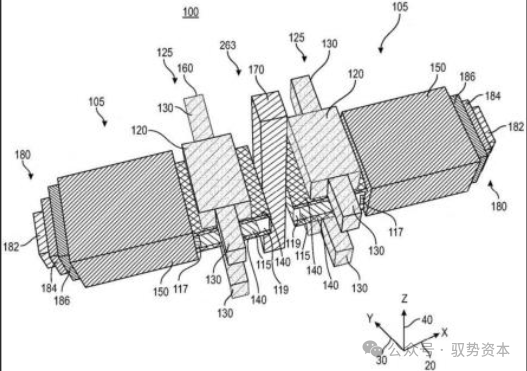

目下,围绕3D DRAM时间的多个主见也曾被提倡,何况关连时间也曾肯求了专利保护。这标明3D DRAM正渐渐从表面主见走向执行应用阶段。主要的DRAM制造商正在积极进行晶圆级测试,以考证和优化3D DRAM的性能和制造工艺。这些测试不仅旨在确保3D DRAM的可行性,还在为大限制分娩和商场奉行作念准备。

行业开端的厂商正加大对3D DRAM时间的研发插足,并通过专利布局来安稳其改日在商场竞争中的地位。这种策略标明3D DRAM时间不仅具有计谋紧迫性,还具备盛大的贸易后劲。在改日,跟着3D DRAM时间的锻真金不怕火和应用场景的扩大,它有望成为存储商场的主流家具,推动通盘存储器行业的创新和发展。厂商们通过专利保护和时间储备,不仅为改日的商场主导权奠定基础,也为时间的发展提供了有劲的保险。跟着时刻的推移,3D DRAM将成为高性能存储惩办有研讨的紧迫构成部分,为各种研讨和数据处理任务提供建壮的支抓。

3.2 3D DRAM的时间挑战

3D DRAM时间诚然展现了诸多上风并取得了权贵进展,但在向大限制应用迈进的过程中,仍然濒临着一系列时间瓶颈和挑战。在从2D DRAM向3D DRAM滚动的过程中,触及的工艺和时间复杂性权贵增多。开端,3D DRAM在容错性和线路性方面濒临挑战。在多层堆叠的3D DRAM中,单个存储单元的故障可能会影响通盘堆叠的可靠性,因此在设计和制造过程中必须特别存眷奈何提高存储单元的容错性,以确保数据的可靠性。这可能需要遴选更先进的纠错时间和冗余设计,以缩小故障对系统合座的影响。

与此同期,信号传输和互连亦然3D DRAM发展中的关节问题。在多层堆叠结构中,数据需要在不同层之间达成高速信号传输,但由于信号传输过程中可能受到蔓延和侵略的影响,奈何提高信号传输的遵守并减少侵略,成为决定3D DRAM性能的关节要素。这需要遴选更先进的互连时间和高频信号处理递次,以保证数据传输的线路性和速率。此外,跟着3D DRAM存储器的层数增多,散热和温度经管问题也愈发隆起。堆叠结构的设计使得热量在存储器里样子易积聚,过高的温度可能导致性能下跌,以致裁汰存储器的使用寿命。因此,奈何有用地散热和经管温度成为了3D DRAM设计中必须惩办的紧迫难题,这可能需要遴选新式材料、优化的封装设计和先进的热经管时间来有用地散播和经管热量。

制造复杂性和成本雷同是3D DRAM发展中不可漠视的挑战。3D DRAM的制造触及到比传统2D DRAM更加复杂的工艺格式,包括垂直纠合和多层堆叠等,这不仅增多了制造的时间难度,还权贵提高了分娩成本。因此,如安在确保性能的同期按捺制形成本,成为3D DRAM大限制贸易化应用的关节问题。此外,封装时间的开端也至关紧迫。由于3D DRAM结构更加复杂,奈何有用地封装这些存储器以鼎沸商场需求是一大挑战。封装不仅需要提供物理保护,还要确保电气纠合的可靠性,并具备精良的散热性能。

在AI、云研讨、自动驾驶等新兴应用的推动下,3D DRAM具有深入的发展前程。改日几年,3D DRAM时间将在堆叠层数的增多、存储密度的莳植、数据传输速率的加速、功耗的申斥以及功能集成等方面不断发展。这些开端将为各个边界带来更高效、高性能的存储惩办有研讨。诚然目下3D DRAM仍处于产业化前期,商场模式尚未皆备了了,但不错想到的是,3D DRAM将成为存储器商场的紧迫迁徙点,为存储厂商提供霸占改日计谋高地的全新机遇。在这一过程中,3D DRAM有望成为推动存储时间创新的紧迫力量。

跟着Windows 11的普及和AI PC的兴起,PC商场的复苏态势权贵。逸想和惠普不断保抓强劲的商地点位,而华硕则凭借游戏PC的强劲弘扬,自满出其在商场上的竞争力。苹果的线路增长也标明其在高端商场的抓续眩惑力。总体来看,内行PC商场正在资格一波更新换代的飞扬,改日几个季度有望抓续增长。

3.3.领头企业3D DRAM布局

(1)在2024年3月的内行芯片制造商峰会Memcon 2024上,三星电子夺目先容了其3D DRAM的开发阶梯图。这一文告标记着三星在3D DRAM时间上的抓续鼓动和计谋布局。早在2021年,三星就已谨慎启动了其3D DRAM开发样子。这次峰会上,三星线路了其改日几年的时间发展权谋和指标。

三星权谋在2025年推出基于垂纵贯谈晶体管时间的3D DRAM早期版块。这种新式时间的关节在于其晶体管结构中,通谈的标的由传统的水平改为垂直,同期遴选一个栅极包裹通谈看成开关。垂纵贯谈晶体管的设计不仅不错权贵减悭吝件的面积占用,还玩忽提高存储密度和性能。然则,这一设计对刻蚀工艺的精度条目更高,对制造过程提倡了更大的挑战。

在2030年,三星还权谋推出更新版块的堆叠式DRAM,这种DRAM将包括电容器在内的扫数存储单元进行垂直堆叠。堆叠DRAM的设计允许在有限的平面空间内充分欺诈Z轴空间,从而在单颗芯片上达成杰出100GB的存储容量。这种设计不仅权贵莳植了存储密度,还玩忽鼎沸日益增长的数据存储需求。

为推动3D DRAM时间的发展,三星早些时候在好意思国硅谷树立了一家新的研发实验室。实验室极力于于开发和优化3D DRAM时间,包括垂纵贯谈晶体管和堆叠DRAM两项关节时间。三星还展示了奈何通过先进的wafer-to-wafer搀和键合时间来制造这些3D DRAM芯片。此外,三星正在探索将后面供电收集(BSPDN)时间应用于3D DRAM,以进一步莳植其性能和遵守。这些时间创新和研发进展标明,三星正积极推动3D DRAM的产业化进度,力争在改日的存储商场中占据开端地位。这些发愤不仅展示了三星在存储时间边界的深结识力,也响应了对改日存储需乞降时间趋势的前瞻性布局。

(2)好意思光公司自2019年开动积极开展3D DRAM的研讨,并在这项时间边界取得了权贵进展。按捺2022年8月,好意思光也曾取得了30多项与3D DRAM关连的专利,这一数目是三星电子和SK海力士等韩国主要芯片制造商的两到三倍。好意思光的这些专利涵盖了3D DRAM时间的各个方面,响应出其在这一边界的时间深度和创新智商。

好意思光合计,3D DRAM将是DRAM时间发展的紧迫标的,并将其视为改日存储时间膨胀的关节格式。为达成3D DRAM的指标,通盘半导体行业正在积极开展关连研讨。这些研讨触及到多个时间边界,包括制造开辟的开发、先进的原子层千里积(ALD)、采用性气相千里积(CVD)以及采用性蚀刻等工艺。此外,对3D DRAM架构的究诘也在不断鼓动,旨在优化存储器的性能和密度。

笔据行业研讨公司Yole的分析,好意思光的3D DRAM专利肯求与三星电子的有研讨有所不同。好意思光的时间有研讨通过转换晶体管和电容器的格式,而不是在存储单元内甩掉额外的电容器。这种递次的中枢在于优化晶体管和电容器的几何设计,以提高存储密度和性能。这种创新的设计念念路可能为3D DRAM时间的达成提供新的惩办有研讨,并推动存储时间的进一步发展。

合座来看,好意思光在3D DRAM时间上的插足和创新,标明其在改日存储商场中的计谋定位。跟着时间的不断开端和专利的积聚,好意思光不仅在时间边界取得了开端上风,也为改日的商场竞争奠定了坚实的基础。这种时间驱动和创新策略,将对存储器行业的发展产生深远影响。

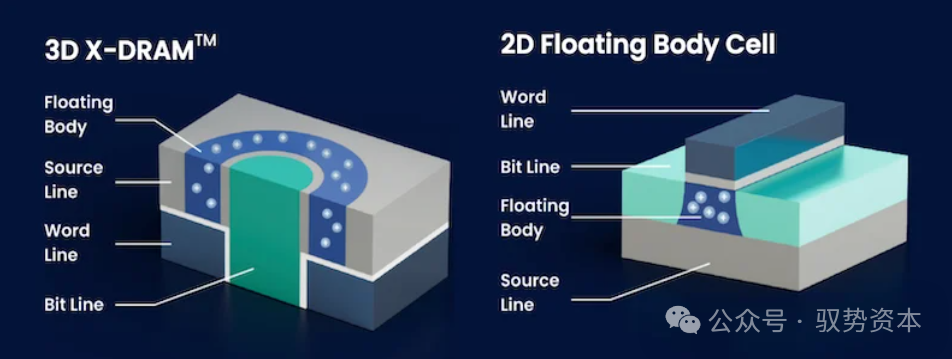

(3)NEO半导体推出了一种名为3D X-DRAM的新时间,旨在打破传统DRAM在容量上的按捺。3D X-DRAM遴选了雷同于3D NAND Flash的单元阵列结构,但其中枢创新在于使用了FBC(无电容器浮体单元)时间。与传统DRAM不同,3D X-DRAM通过在晶体管结构中引入多层掩模,形成垂直堆叠的存储单元,从而达成了更高的存储密度和更低的制形成本。这种设计不仅提高了分娩良率,还权贵减少了分娩成本,使得3D X-DRAM成为搪塞存储需求增长的有用惩办有研讨。

NEO半导体暗意,3D X-DRAM时间玩忽分娩出高达230层的128Gbit DRAM芯片,这一密度是现时DRAM时间的八倍。这一打破性进展使得3D X-DRAM玩忽在相对较小的空间内提供极高的存储容量,从而鼎沸对高性能、大容量存储器的日益增长的需求。特别是,跟着AI应用(如ChatGPT)的快速发展,对存储器的性能和容量条目也在不断莳植,3D X-DRAM的推出恰是为了搪塞这一挑战。

除了在容量上的权贵莳植,3D X-DRAM还惩办了传统DRAM时间在高密度堆叠过程中濒临的挑战,如散热问题和分娩复杂性。其垂直结构的设计有助于更好地经管热量,同期简化了制造工艺,使得时间更加锻真金不怕火和经济。因此,3D X-DRAM不仅在时间层面上提供了创新惩办有研讨,也在商场需求驱动下成为改日存储器发展的紧迫标的。

参考贵府来自:华鑫证券、驭势老本研讨所